# A Novel Asymmetrical Multilevel Inverter for Higher Output Voltage Levels

# PANKHUDI JAIN

Department of Electronics & Communication Engineering, Dr. A. P. J. Abdul Kalam University, Indore Corresponding Author Email: pankhudijain90@gmail.com

Abstract— In this Paper focus on design and achievement of the new topology in a multilevel inverter with a reduction harmonic, size, cost in higher efficiency the main objective of this work a novel three-phase inverter with applicable in induction motor drive in medium voltage application. The main advantage of the new topology is to reduce the THD (Total Harmonic Distortion) lower electromagnetic interference generation and higher output voltage for applicable induction motor drive. This work describes a reduce harmonic in a single phase seven level, Twenty level & Twenty seven level inverter circuit with new level shift pulse width modulation (LSPWM) scheme is purposed. This topology is a combination of a threesingle level full bridge inverter circuit. There are many topologies of multilevel inverters in literature, popular among them are cascaded H-bridge. In general the control methods of these cascaded inverters are designed an assumption of having all dc source voltages same for all H-bridges. The performance of the purposed a novel seven, twenty three, and twenty seven level multilevel inverter with same number of H-bridges is modified with the inherent benefits & isolated DC sources, The multilevel carrier based Level shifted pulse width modulation methods are used in this topology a seven, twenty three, and twenty seven level output voltage wave forms is shown in FFT window. MATLABE/SIMULINK is used to simulate the inverter circuit operation and control signals.

Index Terms—Two Level Inverter, Reduced Switches and Sources, Pulse Width Modulation (PWM), Multi Level Inverters.

### I. INTRODUCTION

The voltage cause inverters create a voltage or a current with levels also 0 or  $\pm$ V dc they are well-known as two level inverters. They require high switching frequency along with various pulse width modulation (PWM) strategies to get a quality output voltage or a current waveform with a minimum amount of wave content, Surrounded by high power and high voltage application, these two stage inverters, on the other hand, have some restrictions in operating at high frequency mainly due to switching devices should be used in such a way as to keep away from problems connected with their series-parallel combinations that are necessary to obtain capability of handling high voltages and currents.

The multilevel inverter [MLI] is a shows potential inverter topology for high voltage and high power applications. This inverter synthesizes numerous different levels of DC voltages to produce a staircase with the purpose of approaches the cleansine waveform. It has high power superiority waveforms, lower voltage ratings of devices, lower harmonic deformation, lower switching frequency and switching losses, higher efficiency, and reduction of dt/dv stresses. It gives the possibility of working with low speed semiconductors but its comparison with the two-level inverter. several of MLI topologies and modulation techniques have been introduced and studied comprehensively. But most accepted MLI topologies are Cascaded Multilevel Inverter (CMLI), Diode Clamp and Flying Capacitor. In this thesis we employ a CMLI that consist of some with not the same DC named as Asymmetric Cascaded Multilevel Inverter (ACMLI) and H-Bridge inverters. It is implemented because these inverters are more modular and simple in creation and have other reward than flying capacitor and Diode clamp.

### II. TYPES OF MULTI-LEVEL INVERTERS

Multilevel inverter is very versatile and is uses for power electronics topology for high power application. The multilevel inverter has a very low electromagnetic interference (EMI),The voltage across the switches is only one half of the DC source voltage, The switching frequency can be reduced for the same switching losses, The higher output current harmonics are reduced by the same switching frequency. It efficiency is high compare to conventional inverter. Multilevel inverter is a most recentoption to execute low frequency based inverters with low output voltage twist. Basic multilevel topologies are of three types.: 1. Diode-Clamped Multilevel Inverter 2 .Capacitor Clamped/Flying Capacitor Inverter 3. Cascade H-bridge (CHB)

Every three topologies of a multilevel inverter can be used in reactive power compensation not including having the voltage unbalance problem. Diode clamping is not ideal in fast capacitor and cascaded inverter design and balancing capacitors are not required in diode clamped and cascaded inverter configuration. In cascaded inverter configuration requires the smallest amount number of components.

The diode clamped topology is also called as a neutral point converter. It was the first widely popular multilevel inverter topology. It is comprehensively used in industrial application this three levels neutral point converter uses capacitor to generate intermediate voltage level and voltages across the switches are only half cycle in dc input. These inverters most commonly used in medium power and high power voltages. In this inverter topology diode is used as the clamping device to clamp the dc bus voltage so the same as to achieve steps in the output voltage. Thus, the major concept of this inverter is to use diodes to bind the power devices voltage stress. The voltage over each capacitor and each switch is Vdc.

A similar topology to the Neutral-Point Clamped Multilevel Inverter topology is the Capacitor Clamped (CC), or FlyingCapacitor, multilevel inverter topology, As a substitute of using clamping diodes it use capacitors to hold the voltages to the desired values. As for the Neutral-Point Clamped Multilevel Inverter,(m-1) number of capacitors on a shared DC-bus, where m is the level number of the inverter, and 2(m-1) switch-diode valve pairs are used. On the other hand, for the CCMLI, instead of clamping diodes, one or more (depending on position and level of the inverter) capacitors are used to create the output voltages. They are connected to the midpoints of two valve pairs on the same position on each side of the midpoint between the valves [3].

**Cascade H-bridge (CHB):** configuration has newly happen to very popular in adjustable-speed drive and high-power AC supplies applications. In each of its three phases, cascade multilevel inverter contains of a series of H-bridge (single-phase full bridge) inverter units. Each one H-bridge unit has its personal DC source, which for an induction motor would be a battery unit, solar cell or fuel cell.

## **III. PROPOSED TOPOLOGY**

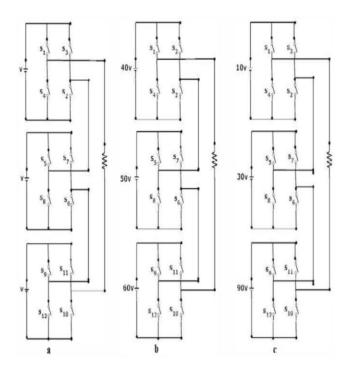

The graphic arrangement of the proposedblock Diagram of Multi Level inverter is shown in figure -3.1. The DC-link is universal for all the phases. Each phase consists of a three-level arrangement connected to common DC-link and a full-bridge with FC coupled at the output of three-level arrangement.

Figure-3.1 Proposed block diagram

Each D.C. source is connected with a single-phase full-bridge inverter. The AC terminal voltages of different level inverters are linked in series. Each one converter level can generate three dissimilar voltage outputs, +Vdc, -Vdc and zero because of dissimilar combinations of the four switches, S1, S2, S3

and S4. The AC outputs of dissimilar full-bridge converters in the identical phase are attached in series such that the synthesized voltage waveform is the addition of the individual converter outputs. Note that the number of output-phase voltage levels is defined in a different way from those of the two earlier converters (i.e. diode clamped and flying capacitor). The number of output-phase voltage levels is formulated by m= 2N+1, where N is the number of DC sources in this topology. A seven-level cascaded converter such that, contents of three full bridge converters and three DC sources. Minimum harmonic deformation can be obtained by controlling the conducting angles on different converter levels. Each H-bridge part generates a quasi-square waveform by phase changing its negative and positive phase legs switching timings. Each switching device for all time conducts 180° (or half cycle) apart from the pulse width of the quasi-square wave. All of the switching devices current stress equal because of this switching method. In the motoring manner, power flows from the batteries from side to side the cascade inverters to the motor.

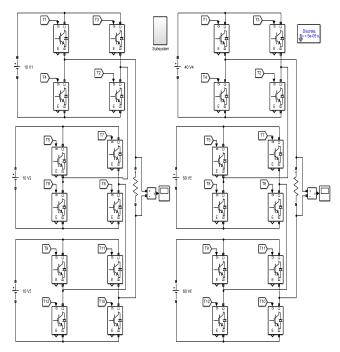

**Figure-3.2** Single Phase Seven-level &Twenty three level H-bridge MLI simulation diagram

The single phase seven level hybrids cascaded multilevel inverter diagram is given Figure 3.2 .this type of the inverter has two types: first one is H-bridge inverter and other is conventional inverter.

The conventional inverter is acting the main inverter and H-bridge inverter is acting the auxiliary inverter. The Main inverter output voltage is either +Vdc/2 (S1isON) or -Vdc/2 (S2 is ON).its connected in series with a full H-bridge that in turn is supplied by a capacitor voltage. If the capacitor is kept charged to Vdc/2, then the output voltage of the H-bridge can take on the values +Vdc/2 (Sa3 &Sa6 ON ), 0 (Sa3,Sa4,Sa5,Sa6 are ON) or -Vdc/2 (Sa4 & Sa5 ON).

### Table-3.1 Switching States of Seven-Level Inverter

TABLE I. SWITCHING SEQUENCE OF 23-LEVEL CHB

| Switches           |     |     |    |    |     |    |    |    |    |     |     |     |

|--------------------|-----|-----|----|----|-----|----|----|----|----|-----|-----|-----|

| Voltage<br>Levels  | \$1 | \$2 | 53 | 54 | \$5 | 56 | 57 | 58 | 55 | 510 | 511 | 512 |

| Vat                | 1   | 0   | 1  | 0  | 0   | 0  | 1  | 1  | 1  | 1   | 0   | 0   |

| 2V <sub>sk</sub>   | 0   | 0   | 1  | 1  | 1   | 0  | 1  | C  | 1  | 1   | 0   | 0   |

| 3V*                | 1   | 1   | 0  | 0  | 1   | 1  | 0  | C  | 0  | 0   | 1   | 1   |

| 4 V*               | 1   | 1   | 0  | 0  | 1   | 0  | 1  | 0  | 1  | 0   | 1   | 0   |

| 5 V.*              | 1   | 0   | 1  | 0  | 1   | 1  | D  | 0  | 1  | 0   | 1   | 0   |

| 6 Vak              | 1   | 0   | 1  | 0  | 1   | 0  | 1  | C  | 1  | 1   | 0   | 0   |

| 7 Vdc              | 0   | 0   | 1  | 1  | 1   | 1  | D  | C  | 1  | 1   | 0   | 0   |

| 9V*                | 1   | 1   | 0  | 0  | 1   | 1  | 0  | 0  | 1  | 0   | 1   | 0   |

| 10 V±              | 1   | 1   | 0  | 0  | 1   | 0  | 1  | C  | 1  | 1   | 0   | 0   |

| 11 V.              | 1   | 0   | 1  | D  | 1   | 1  | 9  | C  | 1  | 1   | 0   | 0   |

| 15 V.              | 1   | 1   | 0  | 0  | 1   | 1  | D  | 6  | 1  | 1   | 0   | 0   |

| 0 V.*              | 1   | 0   | 1  | 0  | 1   | 0  | 1  | 0  | 1  | 0   | 1   | 0   |

| -Vac               | 1   | C   | 1  | 0  | 1   | 1  | 0  | C  | 0  | 0   | 1   | 1   |

| -2 V <sub>ck</sub> | 1   | 1   | 0  | 0  | 1   | 0  | 1  | C  | 0  | 0   | 1   | 1   |

| -3 Vat             | 0   | 0   | 1  | 1  | 0   | 0  | 1  | 1  | 1  | 1   | 0   | 0   |

| -4 Vak             | 0   | 0   | 1  | 1  | 1   | 0  | 1  | C  | 1  | 0   | 1   | 0   |

| -5 Vat             | 1   | 0   | 1  | 0  | 0   | 0  | 1  | 1  | 1  | 0   | 1   | 0   |

| -6 V#              | 1   | 0   | 1  | D  | 1   | 0  | 1  | 0  | 0  | 0   | 1   | 1   |

| -7 V <sub>dt</sub> | 1   | 1   | 0  | Ð  | 0   | 0  | 1  | 1  | 0  | 0   | 1   | 1   |

| -9 Vat             | 0   | 0   | 1  | 1  | 0   | 0  | 1  | 1  | 1  | 0   | 1   | 0   |

| -10 Va             | 0   | D   | 1  | 1  | 1   | 0  | 1  | e  | 0  | 0   | 1   | 1   |

| -L1 Va:            | 1   | 0   | 1  | D  | 0   | 0  | 1  | 1  | 0  | 0   | 1   | 1   |

| -15 Va:            | 0   | 0   | 1  | 1  | 0   | 0  | 1  | 1  | 0  | 0   | 1   | 1   |

Table-3.2 Conducting switches at different levels of output voltage

TABLE II. SWITCHING SEQUNCE OF 27-LEVEL CHB INVERTER

|                               |    |    |    |    | VVI | SKI | ER  |    |     |     |     |     |

|-------------------------------|----|----|----|----|-----|-----|-----|----|-----|-----|-----|-----|

| Switches<br>Voltage<br>Levels | 51 | SZ | 53 | 54 | 55  | 56  | \$7 | 58 | \$5 | 510 | S11 | 512 |

| Vde                           | 1  | 1  | 0  | 0  | 0   | 1   | 0   | 1  | 0   | 1   | 0   | 1   |

| 2V <sub>dc</sub>              | 0  | G  | 1  | 1  | 1   | 1   | 0   | Э  | 0   | 1   | 0   | 1   |

| 3Vde                          | 0  | 1  | 0  | 1  | 1   | 1   | 0   | 0  | 0   | 1   | 0   | 1   |

| 4Vdc                          | 1  | 1  | 0  | 0  | 1   | 1   | 0   | 3  | 0   | 1   | 0   | 1   |

| 5V <sub>dt</sub>              | 0  | 0  | 1  | 1  | 0   | 0   | 1   | 1  | 1   | 1   | 0   | 0   |

| 6Ves                          | 0  | 1  | 0  | 1  | 0   | 0   | 1   | 1  | 1   | 1   | 0   | 0   |

| 7V <sub>ds</sub>              | 1  | 1  | 0  | 0  | 0   | 0   | 1   | 1  | 1   | 1   | 0   | 0   |

| SVa:                          | 0  | G  | 1  | 1  | 0   | 1   | 0   | 1  | 1   | 1   | 0   | 0   |

| 9V <sub>de</sub>              | 0  | 1  | 0  | 1  | 0   | 1   | 0   | 1  | 1   | 1   | 0   | 0   |

| 10Vde                         | 1  | 1  | 0  | 0  | 0   | 1   | 0   | 1  | 1   | 1   | 0   | 0   |

| 11Vd.                         | 0  | 0  | 1  | 1  | 1   | 1   | 0   | 0  | 1   | 1   | 0   | 0   |

| 12Vd:                         | 0  | 1  | 0  | 1  | 1   | 1   | 0   | 9  | 1   | 1   | 0   | 0   |

| 13V4:                         | 1  | 1  | 0  | 0  | 1   | 1   | 0   | 0  | 1   | 1   | 0   | 0   |

| OVde                          | 0  | 1  | 0  | 1  | 0   | 1   | 0   | 1  | 0   | 1   | 0   | 1   |

| -Vete                         | 0  | 0  | 1  | 1  | 0   | 1   | 0   | 1  | 0   | 1   | 0   | 1   |

| -2Vde                         | 1  | 1  | 0  | 0  | 0   | 0   | 1   | 1  | 0   | 1   | 0   | 1   |

| -3Vate                        | 0  | 1  | 0  | 1  | 0   | 0   | 1   | 1  | 0   | 1   | 0   | 1   |

| -4Vde                         | 0  | G  | 1  | 1  | 0   | 0   | 1   | 1  | 0   | 1   | 0   | 1   |

| -5V <sub>de</sub>             | 1  | 1  | 0  | 0  | 1   | 1   | 0   | 0  | 0   | 0   | 1   | 1   |

| -6Vete                        | 0  | 1  | 0  | 1  | 1   | 1   | 0   | 0  | 0   | 0   | 1   | 1   |

| -7V <sub>dk</sub>             | 0  | 0  | 1  | 1  | 1   | 1   | 0   | 0  | 0   | 0   | 1   | 1   |

| -SVds                         | 1  | 1  | 0  | 0  | 0   | 1   | 0   | 1  | 0   | 0   | 1   | 1   |

| -9V de                        | 0  | 1  | 0  | 1  | 0   | 1   | 0   | 1  | 0   | 0   | 1   | 1   |

| -1 CVat                       | 0  | 0  | 1  | 1  | 0   | 1   | 0   | 1  | 0   | 0   | 1   | 1   |

| -1 1V#                        | 1  | 1  | 0  | 0  | 0   | 0   | 1   | 1  | 0   | 0   | 1   | 1   |

| -12Va                         | 0  | 1  | 0  | 1  | 0   | 0   | 1   | 1  | 0   | 0   | 1   | 1   |

| -13Vet                        | 0  | 0  | 1  | 1  | 0   | 0   | 1   | 1  | 0   | 0   | 1   | 1   |

Table-3.1 shows the current orders for different operating modes of seven-level& twenty three level inverter.Generation of pulse width modulation signal formula shown in tabel-3.1 these pulses are given for 24 switches use. In this inverter has 12 switches "Sa1, Sa2, Sa3, Sa4, Sb1, Sb2, Sb3, Sb4Sc1, Sc2, Sc3, Sc4 " for upper lag and 12 switches "Sa11, Sa21, Sa31, Sa41, Sb11, Sb21, Sb31, Sb41, Sc11, Sc21, Sc31, Sc41 for lower lag . The corresponding conducting switches and inverter output voltage levels are given in Table 3.2. It can be understand that the number of conducting switches for each level is very less. This ensures the higher efficiency of the proposed seven-level inverter.

#### **IV. SIMULATIONRESULTS**

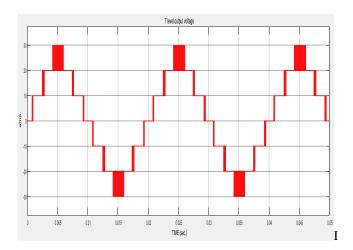

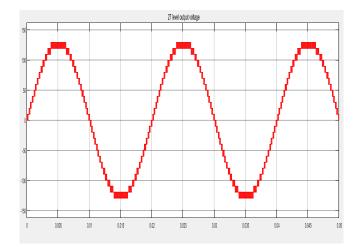

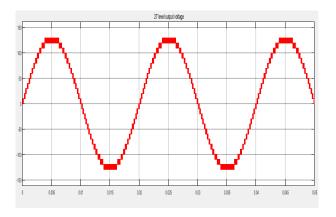

Figure 4.1 output voltage waveform of seven levels MLI

Figure 4.2 output voltage waveform of twenty three levels MLI

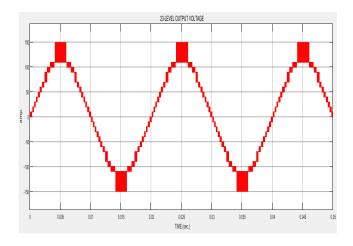

Figure 4.3 output voltage waveform of twenty seven levels MLI

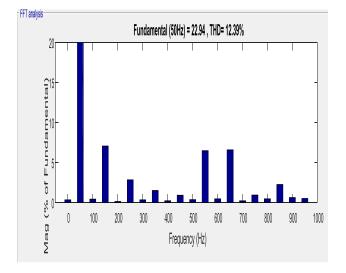

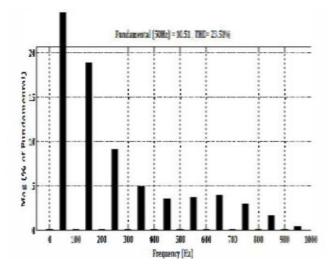

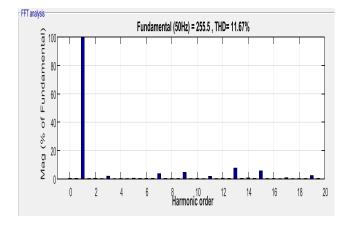

Figure 4.4 FFT analysis of New seven levels MLI output voltage waveform.

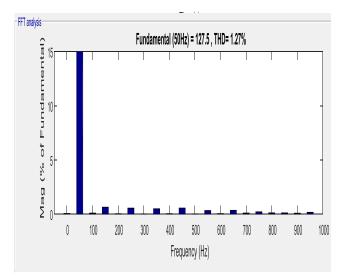

Figure 4.5 FFT analysis of Old seven levels MLI output voltage waveform.

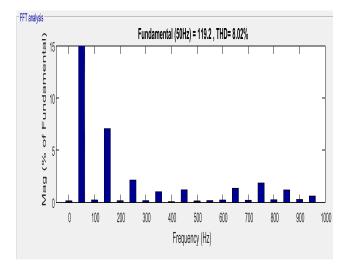

Figure 4.6 FFT analysis of New Twenty three levels MLI output voltage waveform.

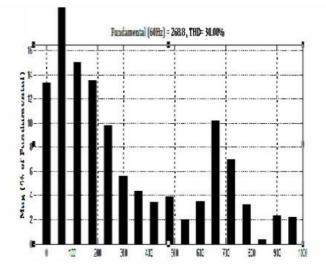

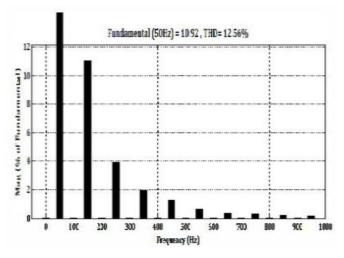

Figure 4.7 FFT analysis of Old Twenty three levels MLI output voltage waveform.

Figure 4.8 FFT analysis of New Twenty Seven levels MLI output voltage waveform.

Figure 4.8 FFT analysis of Old Twenty Seven levels MLI output voltage waveform.

# V. PERFORMANCE ANALYSIS OF SEVEN LEVEL MLI WITH MOTOR LOAD IN PHASE-A

**Figure 5.1** output voltage waveform of twenty seven levels MLI with Induction Motor Load fed.

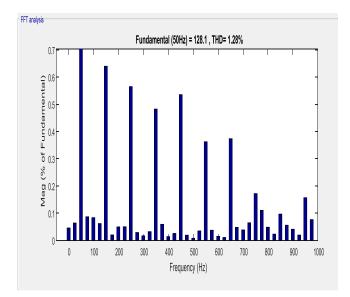

**Figure-5.2** FFT analysis for Oldtwenty seven levels MLI with Induction Motor Load fed.

Figure-5.3 FFT analysis for New twenty seven levels MLI with Induction Motor Load fed.

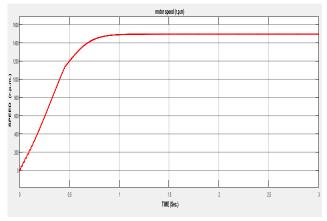

Figure-5.4 Speed characteristics of old (base paper) for MLI fed induction motor load.

Figure-5.5 Speed characteristics of New MLI fed induction motor load.

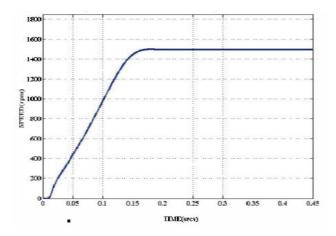

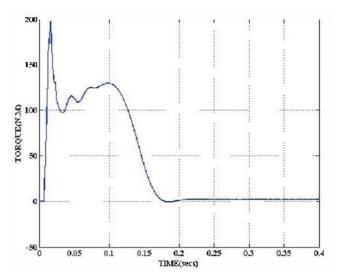

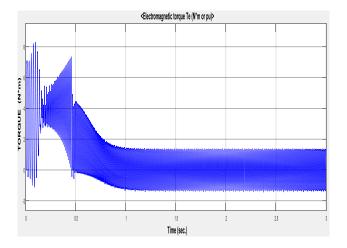

Figure-5.6 Torque characteristics of old (base paper) for MLI fed induction motor load.

Figure-5.7 Torque characteristics of New MLI fed induction motor load.

Proposed H-bridge cascaded multilevel inverter circuit. The topology of an inverter circuit is based on the requirement and range. All topologies have both advantages and is advantages. The two level inverters cost is very low as compared to other conventional inverter topologies. but very high value of THD. Then to reduce THD levels of a inverter voltage waveforms should be increased. And the number of level increases in a inverter then switching losses increased. Theses all above problems can be avoided by hybrid multilevel inverter.

Figure-5.2 & Fig.-5.3 Shows in New & Old (Base paper) THD (total harmonics distortion) value for a proposed 3-Phase H-bridge cascaded multilevel inverter circuit with induction motor load in a seven level. This proposed circuit has THD-11.67% for a seven level output voltage waveform.The topology of an inverter circuit is based on the requirement and range.Figure 5.7 Speed Torque Characteristics of 3-phase IM for a proposed H-bridge cascaded multilevel inverter circuit in a seven level. Fig,-4.7 shows proposed circuit THD-11.67% & fig-4.8 shows old (base paper) circuits THD-24.57% for a seven level output voltage waveform.

### V. CONCLUSION

This Paper work has provided a brief summary of implementation 7, 23 & 27- level multilevel inverter circuit is proposed for more improved output as per the requirement. In this proposed circuit output value of the voltage & THD are minor differences with motor load or without motor load shown Table-6.2. Then also the power quality is improved & converter is large stable. Comparison a (Base paper) Old & New MLI without motor load results in 7, 23, & 27 levels HMLI shown in Table-6.1,

**Table:** 6.1 Comparison a (Base paper) Old & New MLIwithout motor load results in 7, 23, & 27 levels HMLI

| HML<br>INVERTERS      | THD (Total<br>harmonics<br>distortion) | Fundamental Vol,<br>(50 Hz)= |  |  |  |

|-----------------------|----------------------------------------|------------------------------|--|--|--|

| Without motor<br>load | 1.27 %                                 | 127.5 V.                     |  |  |  |

| With motor load       | 1.28 %                                 | 128.1 v.                     |  |  |  |

**Table: 6.2** Comparison a Result With motor load & Without motor load of New HMLI

| H-BRIDGE<br>INVERTER<br>S | OLD (Base<br>paper)THD<br>(Total<br>harmonics<br>distortion) | <u>NEW</u><br>(propose<br><u>d work)</u><br><u>THD</u><br>( <u>Total</u><br><u>harmonic</u><br><u>§</u><br><u>distortio</u><br><u>n)</u> | OLD<br>(Base<br>paper)<br>Fundam<br>ental<br>Vol, (50<br>Hz)= | <u>NEW</u><br>(proposed<br>work)<br>Fundame<br>ntal Vol,<br>(50 Hz)= |

|---------------------------|--------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|----------------------------------------------------------------------|

| 7-level                   | 30.07%                                                       | 12.39 %                                                                                                                                  | 20.88 V.                                                      | 22.94 V.                                                             |

| 23-level                  | 23.5 %                                                       | 8.02 %                                                                                                                                   | 90.51 V.                                                      | 119.2 V.                                                             |

| 27-level                  | 12.56 %                                                      | 1.72 %                                                                                                                                   | 109.2 V.                                                      | 127.5 V                                                              |

#### REFERENCES

- 1. BailuXiao,et.al, "Modular Cascaded H-Bridge Multilevel PV Inverter with Distributed MPPT for Grid-Connected Applications,"IEEE Trans. Ind. Applications.,Vol. 51, No. 2, pp. 1722–1731, 2015.

- 2. Fengjiang Wu, Xiaoguang Li, Fan Feng, HoayBengGooi, "Modified Cascaded Multilevel Grid-Connected Inverter to Enhance European Efficiency and Several Extended Topologies," IEEE Trans. Industrial Informatic., Vol. 11, No. 6, pp.1358–1365, Aug. 2015.

- 3. Marino Coppola, et.al, "An FPGA-Based Advanced Control Strategy of a Grid Tied PV CHB Inverter," IEEE Trans. Power.Electron., Vol. 31, No.1, pp. 806–816, 2016.

- 4. Akira Nabae, Isao Takahashi, Hirofumi Akagi "A new neutral point clamped PWM inverter," IEEE Trans. Ind. Appl, Vol.IA-17, No.5, pp.518-523, 1981.

- S.Ogasawara,H.Akagi, "Analysis of variation of neutral point potential in neutral-point-clamped voltage source PWM inverters," Industrial Applications society annual meeting, Vol.2, pp.965-970, 1981.

- 6. F. Z. Peng and J. S. Lai, "Multilevel Cascade Voltage-source Inverterwith Separate DC Source," U.S. Patent 5 642 275, June 24, 1997.

- Rodriguez, J. Bernet, S.Wu, B., Pontt, J.O., Kouro, 'Multilevel voltagesource-converter topologies for industrial medium-voltagedrives', IEEE Trans. Ind. Electron., Vol. 54, No. 6, pp. 2930–2945, 2007.

- 8. K. Corzine; Y. Familiant, "A new cascaded multilevel H-bridge drive," IEEE Trans. Power.Electron.,Vol. 17, No. 1 pp. 125–131, 2002.

- Cheng-Han Hsieh,et.al, "Design and Implementation of a Novel Multilevel DC–AC Inverter," IEEE Trans. Ind. Applications., Vol. 52, No.3, pp. 2436–2443, May/June 2016.

- 10. Jin-Sung Choi and Feel-soon Kang, "Seven-Level PWM Inverter Employing Series-Connected Capacitors Paralleled to a Single DC Voltage Source," IEEE Trans. Electron., Vol. 62, No.6, pp. 3448–3459, June-2015.

- 11. Arif Al-Judi, Edwin Nowicki, "Cascading of diode bypassed transistor-voltage-source units in multilevel inverters," IET Power Electronics.,Vol. 6, No.3, pp. 554–560, 2013.

- Sridhar R. Pulikanti; Vassilios G. Agelidis, "Hybrid Flying-Capacitor-Active-Neutral-Point-Clamped Five-Level Converter Operated With SHE-PWM," IEEE Trans. Ind. Electron. Vol. 58, No.10, pp. 4643–4653, 2011.

- M.R. Baiju, K. Gopakumar, K.K. Mohapatra, V.T. Somasekhar, "Five- level inverter voltage-space phasor generation for an open-end winding induction motor drive", IEE Proc.-Electr. Power Appl., Vol. 150,No. 5,September 2003.

- Amer M. Y. M. Ghias; JosepPou; MihaiCiobotaru; Vassilios G. Agelidis, "Voltage-Balancing Method Using Phase-Shifted PWM for the Flying Capacitor Multilevel Converter", IEEE Trans. Power.Electron., Vol.29, pp.4521-4531, 2014.